# **TestBench Components**

## **Design and Testbench**

- "Design" ....HDL code....converted as RTL.....goes into IC or SoC

- Design Engineer

- "Test Bench" or "TB" ....HDL (or any other) code...used to verify design

- Verification Engineer

- For Design Engineer....Verilog and SystemVerilog is same

- SystemVerilog is preferred by Verification Engineer

- SystemVerilog = Verilog + A lot of verification supporting features.

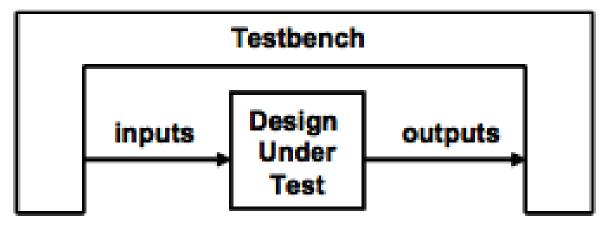

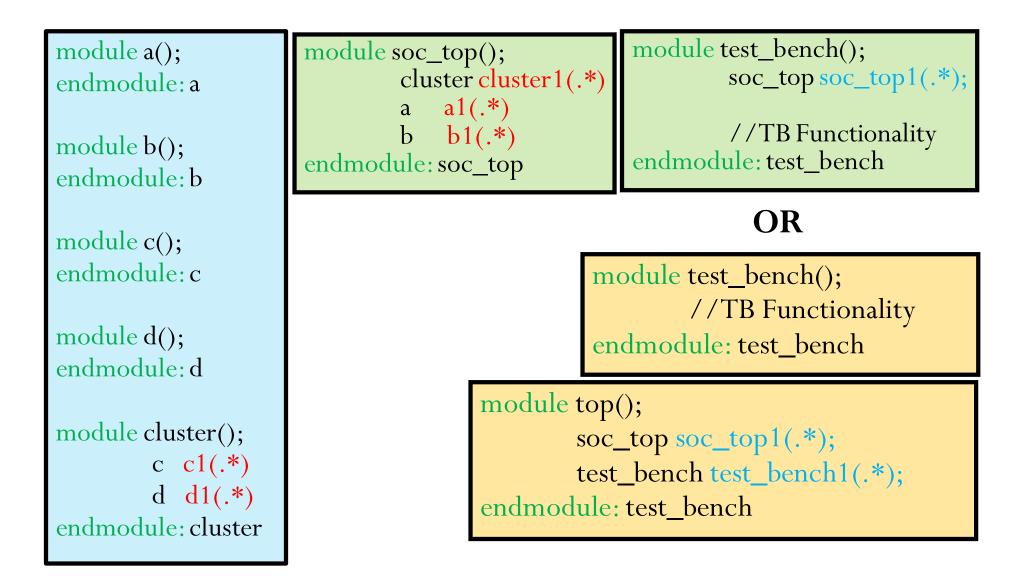

- The design code might contain hierarchical level of modules.

- There will be always a top level module in the design which instantiate the hierarchical modules.

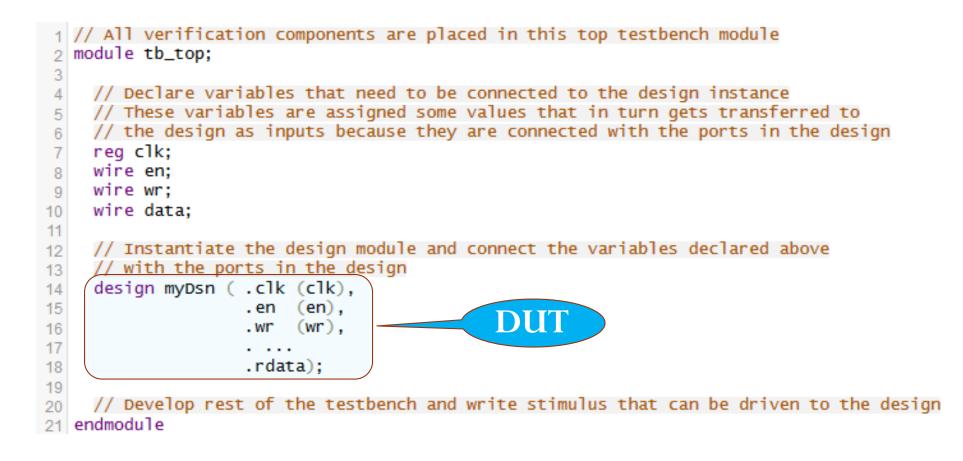

- The Test Bench is again another 'module' in SV.

- The 'Top-level module' of the design will be instantiated in the TB module.

## **Design and Testbench**

#### What is DUT?

### Linear Testbench

- ✓ Linear TestBench is the simplest, fastest and easiest way of writing testbenchs.

- $\checkmark$  This became novice verification engineer choice.

- $\checkmark$  It is also slowest way to execute stimulus.

- ✓ Typically, linear testbenchs are written in the VHDL or Verilog. In this TestBench, simple linear sequence of test vectors is mentioned.

- $\checkmark$  Stimulus code is easy to generate.

- ✓ Small models like simple state machine or adder can be verified with this approach.

## SystemVerilog Testbench Features

- ✓ Constrained random generation built on class infrastructure

- ✓ Universal *randomize()* method

- ✓ In-line random generation (*randomize*() with)

- ✓ Spawn threads (*fork...join/join\_any/join\_none*)

- ✓ Control threads (*process* class methods)

- ✓ Inter-process communication (*mailboxes, semaphores* etc)